# Jeppix Roadmap 2018

THE ROAD TO A MULTI-BILLION EURO MARKET IN INTEGRATED PHOTONICS

# Contents

| Exe | ecutive Summary                    | 3  |

|-----|------------------------------------|----|

| 1.  | Introduction                       | 5  |

| 2.  | Applications                       | 7  |

| 3.  | Business                           | 12 |

| 4.  | Market                             | 16 |

| 5.  | Technology                         | 20 |

| 6.  | Process Design Kit and Library     | 29 |

| 7.  | Photonic IC Design Tools and Flows | 33 |

| 8.  | Packaging and Testing              | 36 |

| 9.  | Equipment                          | 46 |

| 10. | Cost                               | 49 |

| 11. | Public and Private R&D Investment  | 54 |

| 12. | Training and Education             | 57 |

#### Annexes

| About JePPIX            |  |

|-------------------------|--|

| Survey 2017             |  |

| List of Abbreviations70 |  |

#### Publication: May 2018

**The JePPIX consortium** | www.jeppix.eu | coordinator@jeppix.eu JePPIX is hosted by the Photonic Integration Technology Centre | www.pitc.eu

## Executive Summary

InP-based Photonic Integrated Circuits (PICs) have become firmly established in the market place. InP PIC-enabled transceivers accounted for a 1B\$ market share in 2015 and are expected to grow beyond 3 B\$ in 2020. Today the application of PICs is broadening to other markets like fibre sensing, medical diagnostics, automotive (LIDAR) and metrology. JePPIX<sup>1</sup> partners SMART Photonics, Fraunhofer HHI and LioniX International are stimulating this development by offering cost-effective open access to advanced PIC foundry processes in InP and silicon nitride technologies. These photonics companies are the core of a vibrant and growing ecosystem, working in important markets in which Europe holds a lead. The JePPIX organization plays a key role in organizing this eco-system.

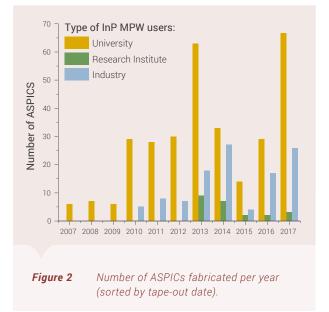

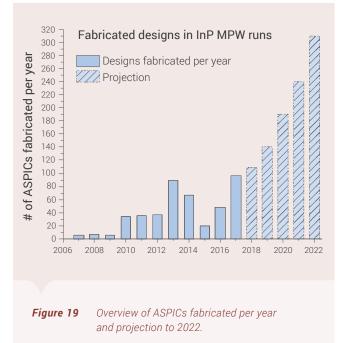

Since 2015, JePPIX has moved from EU-subsidized access to a commercially priced service and after an initial dip the increased awareness and enthusiasm for the technology has enabled JePPIX to manage this transition with an increase in use from businesses. In 2017 alone more than 60 different PIC designs were fabricated in 9 multiproject foundry runs, of which more than 30% were for industrial users, and strong business uptake is foreseen in the next 2-5 years. This roadmap addresses the issues of market expansion, including training and capacity planning needed to support that demand.

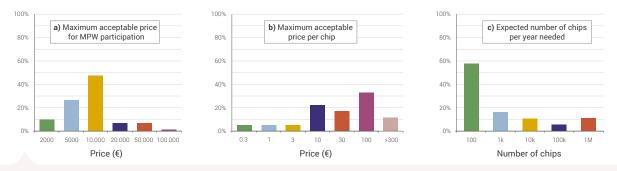

For this 2018 edition of the roadmap, JePPIX has carried out a survey of expert users in order to gauge user requirements and the need for technology developments going forward. Both InP-foundries, SMART Photonics and Fraunhofer HHI, currently offer a full suite of components including high-performance SOAs, lasers, modulators, detectors and a range of passive components. The technology roadmap includes improving component performance to support higher Baudrates (up to 56 GBaud/s), lowering propagation losses, and improving passive component performance by using 193 nm DUV lithography. A continuous effort is foreseen on improving the reproducibility of the processes. For further improvement in performance, a PIC fabrication roadmap is defined for improving the quality of epitaxial growth and adaption of fabrication equipment to the wafer size and mechanical

<sup>1</sup> JePPIX: Joint European Platform for Photonic Integration of Components and Circuits, www.jeppix.eu

properties of InP wafers. This edition of the roadmap also looks further ahead to the arrival of future nodes supporting the integration of photonics and electronics on which several research projects are already running.

The silicon nitride foundry, LioniX International, offers its low-loss SiN integration platform (TriPleX) with a variety of passive components and thermal phase shifters, not only for the infrared but also for the visible spectral range. The technology roadmap foresees further lowering of the propagation losses, the adding of low-power stress-induced (PZT) phase modulators and extending the platform capabilities by hybrid integration of InP and TriPleX PICs. LioniX is also starting to provide open access to its visible light process, to cover applications outside the communications space, including bio photonics and virtual reality.

All three foundries have a Process Design Kit (PDK) with a range of building blocks that can be used by designers, freeing them from the underlying details of the technology. In cooperation with the JePPIX software partners the contents of the PDKs will be substantially extended to include statistical data for component performance and process tolerances. Further, more emphasis will be put on adding manufacturing rules in the PDKs, and to enable the design software to perform automatic Design Rule Checking (DRC) to reduce the chance of designer mistakes. The contents of building block libraries will be extended and an important development is the so-called PDAFlow API, an interface that enables interoperability between different software tools.

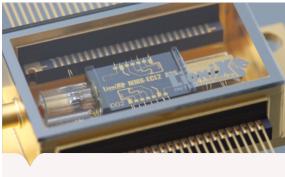

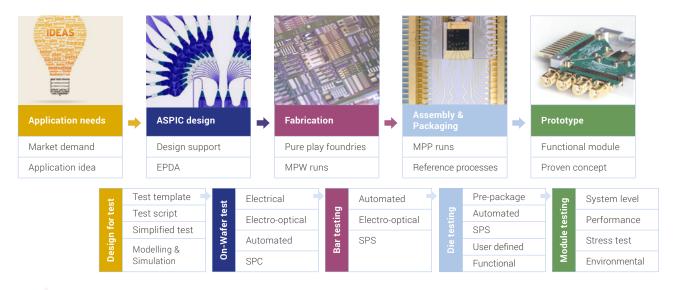

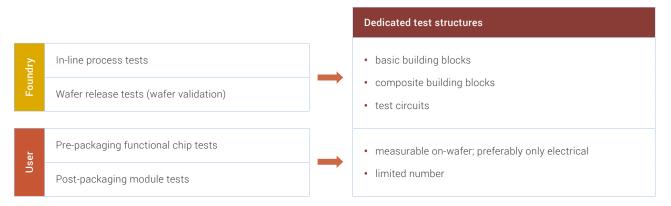

The development of reference packages for prototyping and low-volume production of PICs which are designed according to packaging templates with standardized positions for the electrical and optical ports, is seen as crucial to the development of the PIC market over the next few years. This standardization will also support prototype testing at affordable cost. JePPIX and some of its partners are participating in the PIXAPP Packaging Pilot Line with the ambition to define standardized packaging and test templates and to develop largely automated testing of compliant PICs. The standards are designed such that they support scaling to higher volumes.

The 2018 roadmap synthesizes JePPIX's analysis of the PIC market and market requirements for the coming 2-5 year timescale. Important technology developments required to foster the foreseen market growth are analyzed in many areas, including fabrication processes and equipment, design software, packaging and testing. JePPIX members are also contributing to the AIM roadmapping initiative led by MIT and the World Roadmap for Integrated Photonics, led by Photon Delta.

## 1. Introduction

The PIC-market is rapidly growing, mainly driven by today's 100-400 Gb/s transceivers for telecommunications and datacenters, but other applications will benefit increasingly from the progress in PIC-technology. Four major platform technologies today are Indium Phosphide (InP), Silicon Photonics (SiP), Silica (SiO<sub>2</sub> or PLC) and Silicon Nitride (SiN).

JePPIX, the Joint European Platform for Photonic Integration of Components and Circuits, is a consortium in which Europe's key-players in InP and SiN-based Photonic Integration are cooperating to establish a technology infrastructure for cost-effective open access to standardized (generic) high-performance photonic foundry processes<sup>1</sup>. JePPIX started in 2006 as an open-access technology platform in the European FP6 Network of Excellence ePIXnet. The JePPIX consortium now covers the full chain of PIC-development and manufacturing, it includes partners for chip-manufacturing, PIC design tools and design services, packaging, testing and technology R&D, and it is active in stimulating business development with a large number of companies and researchers being supported by the consortium.

JePPIX is organizing commercial access to its foundry platforms in so-called Multi-Project Wafer runs (presently 11 MPW-runs per year), in a similar way as has been organized in microelectronics since the early eighties (e.g. MOSIS<sup>2</sup>, Europractice<sup>3</sup>). The first JePPIX MPW runs were performed by the COBRA research institute, now the Institute for Photonic Integration (IPI) at TU Eindhoven. Two major European projects started in 2009 and 2010 to transfer the generic foundry approach from the university environment to the industrial platforms of the company Oclaro and the Fraunhofer Heinrich Hertz Institute (HHI). In 2013 the company LioniX joined JePPIX with its silicon nitride (TriPleX) platform. The COBRA process was licensed to the startup company SMART Photonics. JePPIX now provides access to two InP-based foundry platforms (SMART Photonics and Fraunhofer HHI) and one silicon-nitride platform (LioniX International). JePPIX foundries have processed over 400 PIC designs in more than 40 MPW-runs over the last ten years.

- 2 www.mosis.com

- 3 www.europractice-ic.com

<sup>1</sup> M. Smit et al., An introduction to InP-based generic integration technology, Semicond. Sci. Technol. Vol 29 (2014) 083001.

JePPIX has been publishing a roadmap for InP and SiN (TriPleX) based foundry technology approximately every two years (2012, 2013, 2015, and now 2018) and the next edition is planned for 2020. In our 2012 roadmap we predicted that the market for Photonic ICs would exceed 1 B€ before 2020. A recent market report<sup>1</sup> predicts that in 2020 the PIC market will be close to 4B€. Since our previous 2015 edition, we have observed a rapid increase in the use of Photonic ICs for high-speed (100+ Gb/s) transceivers. The transceiver PIC-market is strongly dominated by InP-PICs, and Silicon Photonics products are now becoming established as well, with opportunities opening up for Silicon Nitride. For the coming years the market prospects for these technologies look very good. Silicon Nitride platforms are expected to have impact in particular in biophotonics and microwave photonics.

In the past years we have seen a significant expansion of the PIC ecosystem, with a high number of companies actively exploring the impact of PIC technologies for their own businesses. This will be described in more detail in **chapters 2 and 3**. **Chapter 4** describes the market roadmap. For the InP-based foundries, the development of open access technology has been slightly slower than predicted in our 2015 roadmap. Despite this, most of the roadmap targets for 2016 have been realized and work on the 2018 targets is making good progress. The anticipated InP Pilot Line from the Horizon 2020 program is now expected to start in 2019. In **chapters 5 and 6** we will give a detailed update of the expected progress. The update is based on what we consider technically feasible in combination with the outcomes of a recent survey of user requirements. A summary of this survey is included in Annex 2 to the present roadmap. Progress and required developments of the design software and design resources are discussed in **chapter 7**. Important progress is presently being been made in the field of packaging and testing through cooperation with the PIXAPP Packaging Pilot Line<sup>2</sup> coordinated by JePPIX partner the Tyndall Institute. Packaging and module building are often the first consideration in the adoption of PIC technology and developments in this area are discussed in **chapter 8**. **Chapter 9** describes the required developments in wafer processing equipment. The cost roadmap that we published in 2015 has raised a lot of international attention and discussion. In **chapter 10** we will give an update of this roadmap.

**Chapters 11 and 12** address the requirements for Public-Private funding and for education and training of the scientists and engineers that will be needed to support the expected rapid growth of the field in the coming years.

<sup>1</sup> Lightcounting Market research, Integrated Optical Devices, 2016.

<sup>2</sup> www.pixapp.eu

## 2. Applications Roadmap

So far telecom and datacom applications have been the main driver for the development of PIC-technology. According to market research by LightCounting<sup>1</sup> InP PIC enabled transceivers already accounted for a 1 B€ market share in 2015 and will grow to 3 B€ in 2020. Due to their increased performance and potential for low cost, the use of PICs is now broadening to other application fields representing a significantly larger market.

| PICs? | Market Segment 2015               | %   | B€    |

|-------|-----------------------------------|-----|-------|

| YES   | Production Technology             | 6   | 26,1  |

| YES   | Measurement & Image processing    | 7   | 33,2  |

| YES   | Optical Components and Systems    | 5   | 24,1  |

| YES   | Safety and Defence Technologies   | 7   | 30,2  |

| YES   | Medical Technology & Life Science | 8   | 33,8  |

| YES   | Communication Technology          | 5   | 22    |

| YES   | Information Technology            | 16  | 71    |

| NO    | Displays                          | 26  | 117,6 |

| NO    | Light Sources                     | 7   | 33,4  |

| NO    | Photovoltaic                      | 11  | 49    |

|       | Total photonics market value      | 100 | 447   |

#### **Table 1**Market share of the most important application fields.

Table 1<sup>2</sup> lists the current market share for the most important application fields in photonics and indicates in which fields photonic integrated circuits could apply.

#### Michael Lebby , CEO Lightwave Logic

"There is no doubt that integrated photonics rather than electronics is going to be key to the solution as Moore's Law for electronics begins to saturate. Beyond Moore's Law, we will require huge volumes of reliable, integrated photonic components in optical transceivers over the next decade."

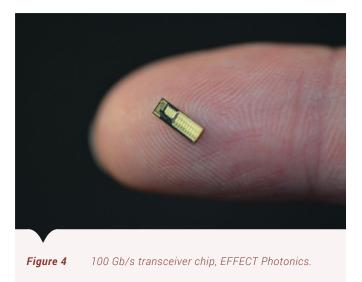

#### Boudewijn Docter , CTO EFFECT Photonics

"The key enabling technology for DWDM systems is full monolithic integration of all photonic components within a single chip and being able to produce these in volume with high yield at low cost, and this is possible with an InP technology platform".

#### Martin Schell, Executive director Fraunhofer HHI

"Generic InP technology makes it possible for us to serve many different customers with development of PIC-prototypes without major investments for those customers. The separation of design and process lowers the entry hurdles significantly, which is especially important for our non-PIC-savvy partners e.g. from sensing applications."

#### José Capmany, Universitat Politècnica de València

"Microwave photonics is evolving from solely defense applications, to encompass civil scenarios through 5G communications, IoT and body/personal area networks. Generic integration InP technologies allowed our group to demonstrate integrated µwave photonics chips, with functions otherwise not possible with discrete components such as beat filters and opto-electronic oscillators."

#### Martijn Heck, PICs group, Aarhus University

"The new eco-system of design software, process design kits and multi-project wafer foundry services, as spearheaded by JePPIX, has enabled a whole new scientific field. Instead of optimizing your photodiode or laser diode by redesigning the epitaxial layer stack, for example, we can now focus on the design of the circuit. This implies that more complex applications are now becoming possible. Moreover, our technology is now closer to the industry, enabling technology transfer out of the lab."

<sup>1</sup> Lightcounting Market research, Integrated Optical Devices, 2016.

<sup>2</sup> www.photonikforschung.de/media/branche/pdf/ UT\_Photonik\_Handout\_English\_bf\_abA7.pdf

*Figure 1* 3" wafer fabricated on the InP generic technology platform of SMART Photonics. Image by F. Lemaitre.

We expect that Photonic ICs will be increasingly applied in the fields of Production Technology (for metrology), Measurement, Optical Components and Systems, Safety and Defence Systems, Medical Technology and Life Science, Communication and Information Technology. In total they cover more than 50% of the total photonics market. In these novel application fields there is a huge potential for both small and larger companies to introduce novel or improved products, equipment or services which use Photonic ICs. We expect that these application fields will lead to a significant increase in the market share of PICs.

Without an open-access foundry infrastructure the costs for developing a PIC are prohibitively large for small companies and universities, and they also form a barrier for larger newcomers in the field that would like to start exploring the potential of PICs without major upfront investments. The open access foundry model used by JePPIX leads to a more than ten-fold reduction of the prototype development cost by sharing the costs of wafer fabrication by many users. Figure 1 shows a 3" wafer, fabricated with the InP generic platform technology of SMART, which shares PIC designs of more than 10 users. Since 2006 the JePPIX foundries have processed more than 400 Application Specific Photonic ICs (ASPICs, see Figure 2). More than 140 were fabricated in the last two years, for applications in telecommunications, data communications, fibre-to-the-home, fibre sensors, gas sensing, medical diagnostics, and metrology. Most of the

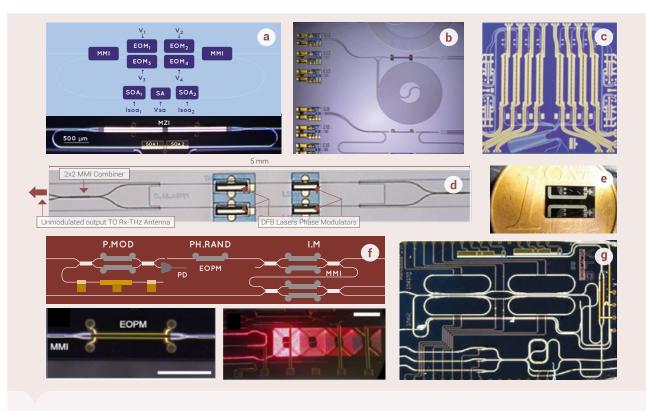

designs were submitted by Universities, but a rapidly increasing part is coming from companies, most of them SMEs. Examples of fabricated PICs are shown in Figure 3, some of them are discussed in more detail on the next page.

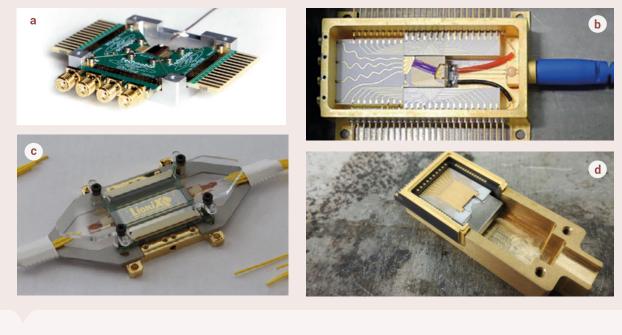

Figure 3 Examples of ASPICS realized for a variety of application fields.

- **a** Optical frequency comb generator.

- **b** Read-out chip for a 4 channel FBG strain sensor for sensing applications.

- c 320 Gb/s WDM transmitter for high-speed data communication.

- **d** Optical THz source for security scanning applications.

- e Quantum random number generator for quantum security.

- *f* Quantum key distribution, can be used for security protocols.

- g Microwave photonics filter for RoF (radio over fibre) applications.

#### Datacom and Telecom

Datacom and telecom are currently the dominant application fields for PICs. High capacity data transmission is important for communication within and between datacentres. The generic monolithic InP open access technology offers the possibility to integrate one or more lasers in a single chip with passive waveguide devices and high-performance modulators and photodiodes, thus reducing the cost of assembly and packaging.

EFFECT Photonics<sup>1</sup>, a start-up in the field of high-speed communication, has developed powerful DWDM optical systems in single-chip technology. One of EFFECT's main products is shown in Figure 4. It is a 100 Gb/s transceiver made of an array of lasers stacked in parallel and connected to MZ modulators that are connected to an AWG which combines the different signals in a single waveguide which is fed to a booster SOA and then connected to an output fibre. DWDM systems are needed to cope with the increasing necessity of speed and bandwidth for data and telecommunications. The EFFECT products have been developed in a generic process, and have

been optimized by customization of the generic process. Such a customization becomes an attractive option for the generic process when larger markets are to be addressed.

#### Sensor readouts

Sensor systems based on fibre Bragg grating interrogators represent a big market in photonics. They have a wide field of applications in terrestrial and aerial transportation, in astronomy and health monitoring. They are attractive because of their reliability, reproducibility, compactness, light weight, immunity to electromagnetic interference and low power consumption. Figure 3b shows a read-out chip for a 4-channel FBG strain sensor developed by the company Technobis on the HHI platform. The device measures a wavelength shift of a fibre Bragg grating in the 1465-1620 nm window. Sub-femtometer resolution is feasible at a sampling rate of 10 kHz. This is several orders of magnitude better than commercially available smallsized wavelength meters.

<sup>1</sup> www.effectphotonics.nl

#### Other Applications

Photonic Integrated Circuits are becoming increasingly important for automotive applications, for example in LIDARs for drones or self-driving cars. InP PICs have the potential to integrate large numbers of optical amplifiers and phase modulators which are important in beam-steering arrays for LIDARS, they have the potential to replace today's more bulky and costly LIDAR systems.

**Figure 5** Ultra narrow bandwidth tunable laser in a hybrid TriPleX technology platform. In the chip, a lasergain section is hybridly attached to a tunable reflector, creating an external-cavity laser. The InP chip contains the first mirror and the gain section, the silicon nitride based TriPleX chip acts as a tunable wavelength-dependent mirror.

For medical applications PICs for Optical Coherence Tomography (OCT) have gained a lot of attention since they can integrate a large part of the sensor system on single a chip, thus massively reducing its size making the device more practical and less aggravating to the patients.

Other emerging application areas are in agriculture where PIC-based spectrometers can be used to analyse the condition of seeds, fruits and vegetables. PIC technology enables low-cost gas sensors for monitoring  $CO_2$  or other type of gases like the levels of methane emitted by the kettle.

We foresee also promising applications by combining InP and TriPleX platform capabilities. As described in Section 5 research is underway to enable low-

cost precision-assembly of InP and TriPleX chips which will bring us a hybrid platform technology in which we can combine the active functionality and high-speed operation of InP technology with the low-loss capabilities of the TriPleX platform. Figure 5 shows an example of a tunable laser fabricated in the hybrid TriPleX technology platform of LioniX. It contains an InP-based optical amplifier fabricated on the HHI platform, which is hybridly coupled to a tunable TriPleX reflector circuit.

## 3. Business Roadmap $\rangle$

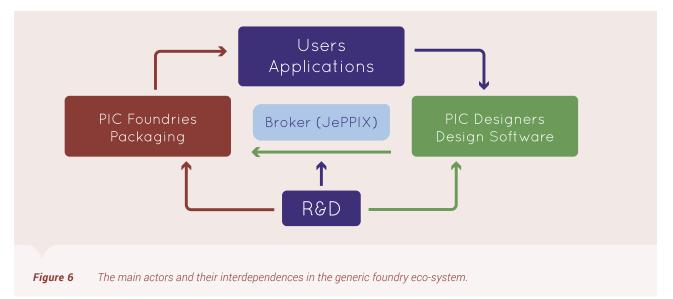

The sustainability of open access photonic integrated circuit technologies requires a combination of competitive industrial players, second-sourcing for customers, and a diverse customer base. The main actors and their interdependencies in the generic foundry eco-system are shown in the schematic of Figure 6. Industrial suppliers are best positioned to accommodate the rapidly increasing demand and provide an agile response to evolving technology requirements. The suppliers form a complex inter-dependent eco-system with foundries, designers, original equipment manufacturers, design tool suppliers, and developers of intellectual property. The key stakeholders will be addressed per domain in this chapter. Due to the complexity of the eco-system, we additionally anticipate a role for public subsidy to maintain open-access for new entrants. Here, the new European initiatives for Digital Innovation Hubs may provide a suitable framework.

JePPIX has proved particularly successful in bringing together the key players in the field of InP and TriPleX based photonic integration and in providing continuity. It provides a focal point for innovators on both the supply and demand side of PIC technology.

#### The business case for PIC users

The largest group in terms of number of businesses and market size is the user base. Generic technologies enable the user to configure the circuit, creating diversity in design and an extensive range of markets. Considerable added value is created in the module for PIC-enabled products. The module can often have a value a factor of ten higher than the PIC itself due to the complexity of additional co-packaged components and the packaging technology. Many developers of PIC-enabled products have limited or no expertise in PIC technology, but are able to add considerable value at the module level. Many businesses have already started to explore PIC technology via JePPIX by prototyping on MPW runs. Hundreds of businesses are following the development of the field either through regular newsletter briefings or via the network of European Application Support Centers established by the PICs4All project to identify the best timing to adopt the technology. Early adopters are already seeing the benefits of mastering the use of PIC technology ahead of their competitors, but the learning curve has been steep while open access technologies have been in the early phases of development. As the technology matures and processes become qualified, future generations of products will benefit from accelerated product development cycles.

#### The business case for PIC designers and design tools

Professional PIC design houses like Bright Photonics and VLC Photonics have been a critical enabler for pioneer businesses and industry innovators. These businesses offer solutions for InP, SiP, SiN, and more besides to create a critical level of business, but specialization may be anticipated as the market takes off. Designers today have been skilled across many platforms and in some cases more than ten platforms, offering both a technology orientation service as well as key skills for creating viable designs ready for fab acceptance. The number of professional designers is increasing fast (but from a low base) as the number of businesses seeking to evaluate prototypes increases. This enables users and Original Equipment Manufacturers (OEMs) to access the technology quickly and with a lower risk, without skilling-up their own employees or recruiting from a relatively small talent pool. Close relationships are developing between professional designers and fabless/ labless SMEs, mid-sized businesses and corporations, guiding product development from early R&D phases to pilot production. The design house offers an attractive business model for skilled PhD graduates trained in the field as capital investments are currently relatively low. The operating costs are dominated primarily by software licenses and personnel costs.

Training programs such as those operated by JePPIX, and the wider access of university research groups to PIC technologies, will be instrumental to growing the talent pool and stimulating innovation. An emerging need for test services may also provide business opportunities for new professional services, and some design houses have also expanded their portfolio of services to testing.

Photonic design tools are numerous, addressing physical properties, interconnection, dynamics, layout, all the way through to system level prediction. Often even the choice of software package requires considerable skill to generate the relevant insight and viable design. Depending on the precise requirement, a complex combination of tools can also be needed motivating activity now in design automation. A number of JePPIX partners and software vendors address the challenge of developing circuit design tools with increasingly accurate building block representations and improved interconnectivity. A number of leading developers have joined the PDAflow initiative for photonic design automation with this objective in mind. A range of tool development opportunities are arising with a number of designers requiring a seamless environment for package, electronics and photonics. As technology matures, the accuracy of predictive design becomes a higher priority, and design for manufacture, showing the impact of manufacturing tolerance to the designer before tape out, becomes increasingly important. A significant number of software vendors already support process design kits provided by JePPIX foundries for increasingly accurate component and circuit level prediction. Standard templates for package and test are also becoming available for circuit layout tools.

#### The business case for foundries

The PIC foundries are the enablers of this rapidly evolving market. Forecasts are imprecise, but current indications are that the high PIC-enabled market penetration level (by value) observed for telecom transceiver technologies is likely to be replicated in a number of additional, larger market segments over the next five years. Data centre interconnects are the most immediate product-class which can benefit from high performance, low-energy products and open-access technology enables new entrants to develop PIC technologies for such markets. A robust generic foundry able to serve many markets does however require considerable up-front investment. The revenue becomes available only after the platform becomes sufficiently mature for the qualification of volume products. Precedents from the microelectronics sector shows that the foundry model is both profitable, sustainable, and enables a diverse and profitable industry around it in the longer term, but the starting phase can be several years. Fluctuations in load are an important factor in

the foundry business model, necessitating diversity in markets. We anticipate a continued mix of in-house manufacturers, integrated device manufacturers and pure-play foundries. A diverse range of customers enables dips in one market segment to be compensated by opportunities in others. The generic model is expected to give pure-play foundries an advantage in terms of accelerated design cycles for new entrants and new designs. In this sense, the open access foundry acts as a public good, enabling access to those outside the immediate industry. Nonetheless, the longer term sustainability of pure play foundries will also require a critical mass of volume products.

Packaging remains a barrier-to-entry to a number of users. Indeed, the packaging is often the starting point for a range of users who are otherwise technology-agnostic. The diversity in packaging specifications has so far fragmented demand, creating a barrier to entry for both suppliers and potential customers. JePPIX partners play a key role in defining package layout templates with a minimum set of standards to enable sufficient volume for tooling, processes and singulation such that the pricing for prototype packages approaches a viable level. JePPIX cooperates closely with the PIXAPP Packaging Pilot Line which is identifying business models and processes for volume scaling of standardised packages.

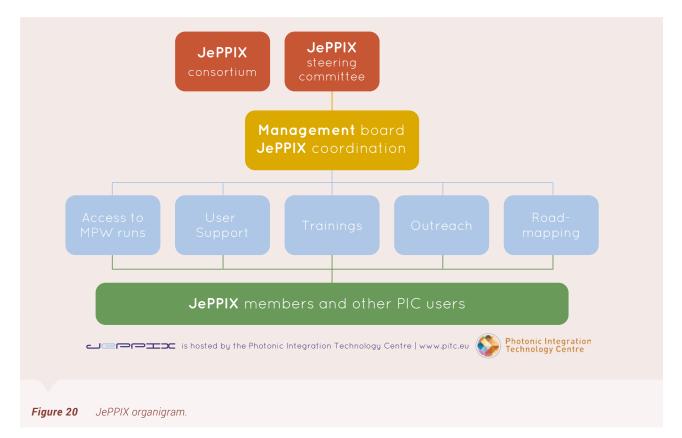

#### The business case for JePPIX as a broker

The eco-system requires both an orchestrator and an access point for customers who look for ease of access through a one-stop shop. A central organization is crucial for effective coordination of the whole eco-system, providing a supply chain to suit the needs for businesses and researchers starting out with PIC-enabled product development. JePPIX is playing such a role by addressing the following tasks:

- Combining designs from different users in Multi-Project Wafer (MPW) runs. The costs of R&D runs can be shared by many users, which leads to a dramatic reduction of the entry costs.

- Enabling the same processes to run independently of design. This decouples process-centering from product development, enabling a ramp up in time through technology readiness levels which is increasingly independent of any given product.

- Organizing documentation and training courses for the available foundry processes. Enabling ever increasing agreement between design tool predictions and fabricated chip performance.

- Reaching out to potential users and mentoring designers through the decision process and design-fab-package-test flow.

- Setting the strategic roadmap and providing leadership in this new technology sector.

JePPIX brokering operations empower the designer through web-based services, as well as technical orientation and training. As the number of businesses increases, and the products evolve, there will be opportunities for customers to configure value chains to their own needs, identifying the functions and services which best suit their own products. The services are currently focused on prototyping, but an increasing demand for product engineering and pre-production will require further scaling in support and documentation.

The brokering operation exists for the benefit of the eco-system and is not intended to be profit-making. In much the same way as for Europractice and MOSIS, there will be some reliance on subvention to maintain a skilled staff able to engage with new entrants and first users, while contributions to brokering costs from the suppliers will support activities for customers transitioning to small series production and pre-production.

The market potential is captured in terms of the high-growth predictions for markets leveraging photonic technology more generally, the recent breakthroughs for InP PIC technologies for telecommunications more specifically, and the uptake in the number of businesses using open-access technologies. We use a combination of published market data for custom InP PIC solutions and insights from JePPIX services to predict market penetration for the open access generic model.

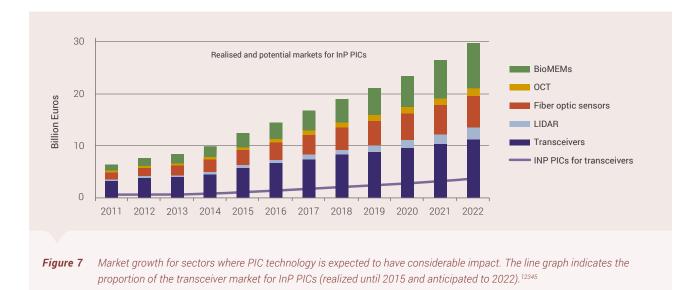

InP-based PICs have become firmly established in the market place, with suppliers including Oclaro, Finisar, Lumentum, Infinera and Sumitomo shipping complex PIC-enabled products today. As shown in figure 7, besides other fields where PIC technology is becoming meaningful, InP PIC enabled transceivers already accounted for a 1 B€ market share in 2015 according to market research by LightCounting and the technology is predicted to account for a 15% transceiver market share by value (5% by volume) in 2018. The breakthrough has been made with the roll-out of 100Gb/s per wavelength links, and the indications are that InP PIC market share will continue to increase with particular impact where performance is critical.

The roll-out of open-access generic integration technologies enables the technology to be exploited in new sectors. The most commonly acknowledged market sectors addressable by PIC technologies are summarized in terms of market growth in the figure on the next page. The front-runner market is transceiver technology, which currently receives considerable attention due to a pressing need from internet traffic growth and accelerated data center deployments. Medical segments such as optical coherence tomography (OCT) through to BioMEMs technology, also see considerable growth and are well positioned to adopt InP PICs and also TriPIeX technologies. Fibre-optic sensing offers a considerable growth opportunity with drivers from the oil industry as well as structural engineering, industrial metrology and aerospace. Compound annual growth rates (CAGR) of order 10% to 20% are observed for photonic solutions in such markets. The increased need for free-space mapping and ranging is driving down the costs of LiDAR technologies, with likely impact in assisted driving, robotics, vision and virtual reality systems. These markets are anticipated to be further out in time, but the technology complexity required is motivating developments now.

For a broader market survey, the Market Research Study Photonics 2017 has been updated by the European Photonics21 public private partnership, breaking sectors out to production technology, measurement and machine vision, medical technology and life sciences, information technology, optical communications, flat panel displays, lighting, defense photonics, optical systems and components and photovoltaics. The global market for Photonics products in 2015 accounted for € 447 billion, growing at a compound annual growth rate of 6.2% from 2011-2015. While sectors such as flat panel displays, lighting and photovoltaics technologies have become commoditized, there remains considerable opportunity for innovation through photonic integration in the remaining sectors, all of which show solid growth.

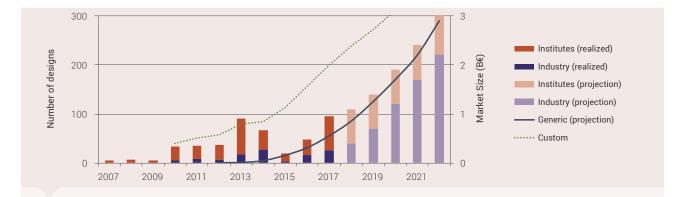

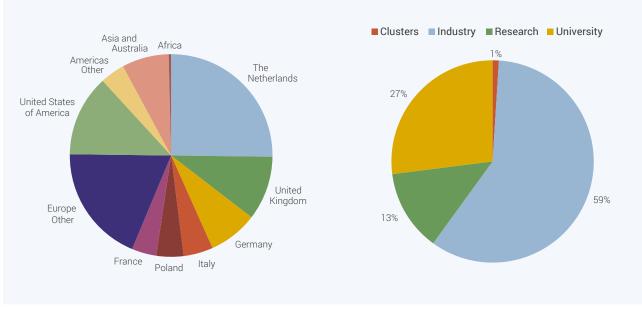

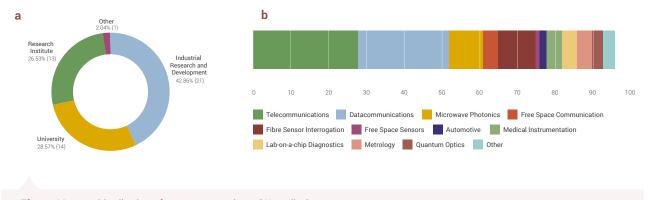

The ramp up in the numbers of designs is particularly important when evaluating the status of market development. The figure opposite shows the ramp up in terms of number of unique designs and also the origins of the designs.

The designs being voluntarily disclosed during the tape out cover a broad range of potential markets. (Note that designers are not required to disclose their domains of interest). A number of circuits can be classed as communications devices, from telecommunications and data-communications to microwave photonics and free space communications. Sensor interrogators have been designed for fibre optic sensors and free space sensing. Prototyping has also been performed for medical instrumentation, lab-on-chip diagnostics metrology and automotive devices through quantum optics.

<sup>1</sup> Optical Coherence Tomography for Healthcare and Life Science: Technology and Market Trends, Tematys, September 2014 tematys.fr/Publications/en/oct/37-optical-coherence-tomography-for-healthcare-and-life-science-technology-and-market-trends.html

<sup>2 2015</sup> Photonic Sensor Consortium Market Survey Report, Information Gatekeepers Inc, March 2015 igigroup.com/st/pages/photonic\_sensor\_report.html

<sup>3</sup> BioMems: Microsystems for Healthcare applications, Yole May 2016, slideshare.net/Yole\_Developpement/sample-bio-mems-2016-final

<sup>4</sup> Market and Technology Briefing: Lidar Technologies and Applications, Yole, EPIC 2017 epic-assoc.com/market-technology

<sup>5</sup> Integrated optical devices: Is Silicon photonics a disruptive technology? Lightcounting market research 2016 lightcounting.com/Silicon.cfm

*Figure 8* Development of the application market enabled by ASPICs with projection of growth in volume to 2022. The bar chart shows the increase in JePPIX designs. The dashed line shows the market growth for custom InP transceiver PICs<sup>5</sup>. The solid line shows the market growth predictions made in the 2015 roadmap. Here a delay is foreseen because the prediction assumed a Manufacturing Pilot Line starting in 2016, which is delayed to 2019.

JePPIX has now provided access for over ten years, transitioning from a purely academic activity to an industry dominated activity. The figure above shows a steady increase in tape-outs up to 2015. Here there is a drop-off at the end of two particularly important European projects (EuroPIC and PARADIGM), and a gap until a widely anticipated Pilot Line program. None-the-less, there has been a steadily increasing interest from businesses creating prototypes using the semi-commercial services.

In our earlier editions of the roadmap we specifically addressed the role of generic integrated technology and did not account for the role of incumbent platforms which were custom-product focused. This was considered to be a reasonable approach as the focus and value for generic technology is in enabling the accelerated adoption for PICs in new markets. Market size projections from the 2013 and 2015 roadmaps still provide a valuable guide to how the market may be expected to evolve. The first movers for PIC technologies have been companies with in-house PIC technology and they have been able to focus technology developments on the fast growing communication markets, leading to multi-billion Euro revenues a couple of years ahead of the forecasts for generic platforms. We now anticipate an acceleration in uptake with the European Pilot Line initiative planned for 2019. The diversity of emerging designs across multiple dynamic market sectors gives considerable confidence for a take-off in the not too-distant future. We see increasing activity for industry designers repeating and fine-tuning designs as they transition from an exploratory phase to a product qualification trajectory.

## 5. Technology Roadmap

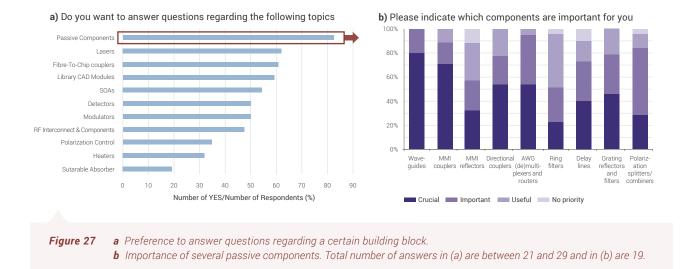

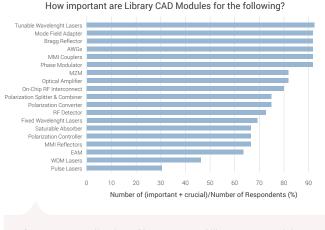

As a result of significant investments in the development of foundry technology infrastructure, Europe has made substantial progress in this new way of working. The standardized open-access technologies that are provided by the two InP foundries SMART Photonics, Fraunhofer HHI and the SiN foundry LioniX International underwent steady improvements over the past years and have increased their range of offering. In this section we give an overview of the present status of the foundry capabilities, indicate where the technology goals from the previous roadmap were met and make a prediction for the status in 2020 and 2022. The predictions also take into account the results from a survey (presented in detail in Annex 2) that was filled out by more than 50 expert PIC users about their specific technology needs.

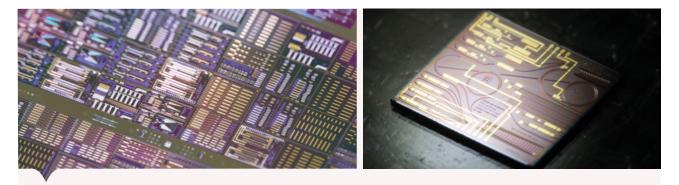

Figure 9 Panoramic view of a processed InP multi-project wafer (left) and a PIC after chip singulation (right). Image by F. Lemaitre.

#### Present Situation and Integration Trends

Presently, all three foundry partners offer commercial or semi-commercial access to their foundry processes through PDKs and have multiple MPWs per year each. Fraunhofer HHI and SMART Photonics both provide a full range of active and passive components, including lasers, detectors, modulators and passive elements, monolithically integrated on InP substrate. The TriPleX platform offers very low-loss passive components in combination with thermo-optic and piezo-electric elements and is well suited for hybrid integration with InP active components to form high performance lasers and interferometers. Different approaches for platform co-integration are being pursued, such as heterogeneous and hybrid approaches. These co-integrated future nodes are briefly discussed at the end of the section.

#### Present Capabilities

When comparing the present capabilities of the platforms with the predictions from the last roadmap release, we observe significant progress: most of the targets have been met. The list of building blocks available is shown in Table 2. In the following, we present the current technical capabilities of the generic platforms.

**The Fraunhofer HHI platform** supports very high-speed photodetectors, spot-size converters (SSCs), thermooptic phase modulators and a variety of passive waveguide components. Recently transmitter components have been added: gain elements/SOAs, DFB lasers, DBR lasers, tunable gratings, EAMs and current-injection phase modulators. Furthermore, polarization splitters and converters to enable on-chip polarization handling are available. The RF detectors exhibit an internal responsivity of 0.9 A/W, a mean dark current of around 1 nA, and an electro-optical bandwidth of 40 GHz. SSCs provide 1.5 dB coupling loss to a cleaved Standard Single Mode Fibre. Waveguide propagation loss varies between <1 dB/cm for low-contrast waveguides to 2 dB/cm for high-contrast waveguides. MMI couplers and AWG de/multiplexers have typical excess losses of 0.5-1 dB and 2-3 dB, respectively. The current-injection phase modulators show 5 mA half-wave current values. The EAMs are characterized by > 20 dB static extinction and > 20 GHz bandwidth. DFB lasers exhibit threshold currents of around 10 mA and optical output power of > 20 mW (@100 mA) in integrated configuration with modulation bandwidth approaching 20 GHz at 100 mA bias current. SOA elements provide around 90 cm<sup>-1</sup> gain and saturation power of 2 mW per 100µm device length. Insertion loss of the polarization rotator devices is ~1 dB with > 20 dB extinction. The platform is built on semi-insulating substrates to provide full electrical isolation of all the functional elements, and offers MPW runs on 3-inch wafers.

**The SMART Photonics platform** offers optical amplifiers, RF modulators, detectors and a variety of passive components. The SOAs provide up to 70 cm<sup>-1</sup> gain and more than 20 mW saturation power. The phase modulators have been enhanced to support 20 GBd with 8 Vmm efficiency. More compact electro-absorption modulators operating with >20 GBd have been added as well. Detectors have > 0.85 A/W responsivity and 30 GHz bandwidth. Waveguide propagation losses are 2 dB/cm. Tunable DBR gratings with 50 cm<sup>-1</sup> coupling coefficient are available for laser designs. In addition, ArF-scanner lithography has been introduced to the MPWs, which supports significantly improved performance for devices which require high resolution (e.g. AWGs) and high uniformity and reproducibility (e.g. interferometers). The platform has moved from 2" to 3" wafer size to improve capacity and uniformity.

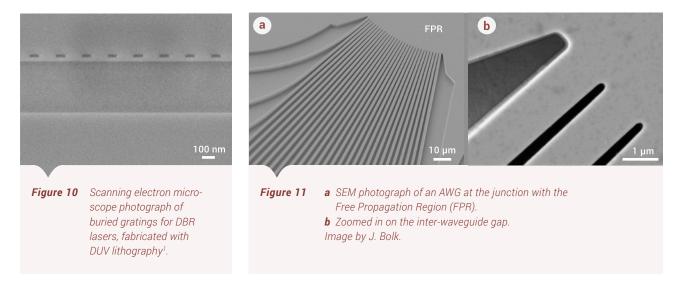

The introduction of DUV lithography combines high resolution (<100 nm) with the possibility for volume production. It enables 20 nm critical dimension variation of the lithography which enables improved waveguide phase control. DBR gratings, for example, (Figure 10) have been demonstrated, as well as AWGs with waveguide gaps of 100 nm (Figure 11) which reduces the loss significantly. AWG central channel insertion losses close to 0.5 dB have been measured with a cross talk level lower than -25dB for all channels.

**The TriPleX platform** offers low-loss straight waveguides, bends, S-bends, offsets, splitters, spot size converters, lateral tapers and thermo-optic phase shifters. Combinations of these building blocks allow, for example, the creation of microwave photonics ASPICs through combinations of Mach-Zehnder interferometers and micro ring resonators. The current platform has guaranteed losses below 0.5 dB/cm and results reported by customers have been as low as 0.1 dB/cm for the high confinement waveguides. Currently the PDK for visible light is under development in the PIX4Life pilot line project and it will be open to commercial users in 2018.

<sup>1</sup> L.M. Augustin, "InP-Based Generic Foundry Platform for Photonic Integrated Circuits", IEEE Journal of Selected Topics in Quantum Electronics, 24(1), 2017.

| Component                         | Target specification          | Fraunhofer HHI                             | SMART Photonics                              |

|-----------------------------------|-------------------------------|--------------------------------------------|----------------------------------------------|

| Lasers and Amplifiers             |                               |                                            |                                              |

| SOA                               | Gain                          | 92 cm <sup>-1</sup> @7000A/cm <sup>2</sup> | 70 cm <sup>-1</sup> @ 9000 A/cm <sup>2</sup> |

|                                   | Saturation Power              | >3dBm                                      | 13dBm                                        |

| DBR grating                       | Tuning range                  | 4 nm                                       | *                                            |

| DFB laser                         | Tuning range                  | 4 nm                                       | *                                            |

|                                   | Output power                  | 3 mW @ 150 mA                              |                                              |

| DBR laser                         | Tuning range                  | 4 nm                                       | *                                            |

|                                   | Output power                  | 3.5 mW @ 150 mA                            | 10mW @ 100mA                                 |

| Isolation section                 |                               | yes                                        | yes                                          |

| Modulators                        |                               |                                            |                                              |

| Thermo-optic phase modulator      | Loss                          | 2 dB/cm                                    | *                                            |

|                                   | I <sub>π</sub> x L            | 20 mA x mm                                 |                                              |

| Current injection phase modulator | Loss                          | 2dB for 100-200 µm                         | <0.5 dB for 2 mm                             |

|                                   | I <sub>n</sub> x L            | 20 mA x mm                                 | t.b.d.                                       |

| Electro-Optical phase modulator   | Loss                          | *                                          | <0.5 dB for 2 mm                             |

|                                   | Bandwidth                     |                                            | 8 GHz                                        |

|                                   | U <sub>π</sub> x L            |                                            | 8 V x mm                                     |

| PIN photodiode                    |                               |                                            |                                              |

|                                   | 3 dB bandwidth                | >35 GHz                                    | >30 GHz                                      |

|                                   | Dark current                  | 10 nA @ -2 dV                              | <25 nA @ -2 V                                |

|                                   | Responsivity                  | 0.8 A/W                                    | >0.85 A/W                                    |

| Passive components                |                               |                                            |                                              |

| Straight Waveguide                | Loss                          | <2 dB/cm                                   | 2 dB/cm                                      |

| Arc waveguide                     | Minimal radius                | 150 µm                                     | 100 µm                                       |

| Spot size converter               | Loss                          | 2 dB to cleaved SSMF                       | *                                            |

| 1x2 MMI coupler                   | Loss                          | <1 dB                                      | <1 dB                                        |

| 2x2 MMI coupler                   | Loss                          | <1 dB                                      | <1 dB                                        |

| 1x2 MMI reflector                 | Loss                          | *                                          | 1.5 dB                                       |

|                                   | Reflectivity                  |                                            | 35%                                          |

| 1x1 MMI reflector                 | Loss                          | *                                          | 1 dB                                         |

|                                   | Reflectivity                  |                                            | 80%                                          |

| Polarization splitter             | Loss                          | <4 dB                                      | *                                            |

|                                   | Polarization extinction ratio | >25 dB                                     |                                              |

| Polarization converter            | Loss                          | <3 dB                                      | *                                            |

|                                   | Extinction                    | >10 dB                                     |                                              |

| Component                  | Quantity                             | Specification |  |  |

|----------------------------|--------------------------------------|---------------|--|--|

| Passive waveguides         |                                      |               |  |  |

| Straight waveguide         | Propagation Loss                     | 0.5 dB/cm     |  |  |

| Arc waveguide              | Propagation Loss                     | 0.5 dB/cm     |  |  |

| Tapered waveguide          | Loss                                 | 0.5 dB/cm     |  |  |

| S-bend waveguide           | Loss                                 | 0.5 dB/cm     |  |  |

| Connectors                 | Loss                                 | 0.5 dB/cm     |  |  |

| Passive components         |                                      |               |  |  |

| Spot size converter        | 1/e <sup>2</sup> Mode Field Diameter | 10 µm         |  |  |

| Y junction                 | Loss                                 | 0.5 dB        |  |  |

| Directional coupler        | Loss                                 | 0.5 dB        |  |  |

| Modulators                 |                                      |               |  |  |

| Phase modulator            | Loss                                 | 0.5 dB/cm     |  |  |

|                            | Ρ <sub>2π</sub>                      | 500 mW        |  |  |

| Phase modulator (arc-type) | Loss                                 | 0.5 dB/cm     |  |  |

|                            | Ρ <sub>2π</sub>                      | 500 mW        |  |  |

| Electrical elements        |                                      |               |  |  |

| DC pad                     | Width                                | 100 µm        |  |  |

| DC bond pad                | Size                                 | 500 µm        |  |  |

| Heaters                    | Radius                               | 100 µm        |  |  |

| T junction                 | Size                                 | 500 µm        |  |  |

Table 3List of building blocks offered at the close of 2017<br/>for the TriPleX MPW runs.

#### Roadmap 2020

In 2020 the SMART Photonics and Fraunhofer HHI platforms plan to offer an extended library of components and provide statistical data of building blocks and wafer verification data.

The Fraunhofer HHI platform will provide increased performance and reproducibility. In 2020 it will be capable of supporting a Tx/Rx symbol rate of 56 GBd on the Tx side accomplished by electro-absorption modulators. Tunable lasers with wider tuning range and lower linewidth will be introduced and advanced polarization handling devices will be available for implementing polarization-multiplexing and polarization diversity functionalities. Out-of-plane coupling mirrors (45°) will be available allowing for automated on-wafer measurement of PICs. Aluminium-based active devices will be added to the platform for more robust performance at high temperature. All building blocks will have statistical performance data.

**The SMART Photonics platform** will provide more functionality by adding spot-size converters (< 1dB loss) and high-speed RF interconnects (> 60 GHz). Together with further bandwidth and efficiency improvements in the modulators and detectors, the platform will be well suited to address high-speed Tx/Rx applications. Both EAMs and MZMs will support 40 GBd operation with < 3 V drive voltage and < 5 Vmm efficiencies. Detectors will have 30 GHz bandwidth and balanced configurations will be supported. This is complemented with simple electrical passive elements such as resistors and capacitors. The option to choose some of the epitaxial material systems will be available as well.

**The TriPleX platform** will add more advanced building blocks to its current library and optimize the waveguide further to an even more robust waveguide cross section. This will be implemented as a PDK upgrade. Structures like AWGs and Micro Ring resonators are on the roadmap of LioniX for implementation in the platform. In addition the implementation of stress induced (PZT) tuning elements in the PDK is foreseen to enable low power tuning of the TriPleX waveguides. LioniX will also start offering the implementation of narrow linewidth light sources in their PDK by offering hybrid integration with InP including packaging. The guaranteed loss will be lowered close to the best-case reported value of 0.1 dB/cm.

#### Roadmap 2022

InP platforms will reduce their passive waveguide losses to < 1 dB/cm and have supporting building blocks for RF and DC interface connections.

**The Fraunhofer HHI platform** will be further enhanced with high-speed (56 GBd) Mach-Zehnder type modulators. Production will be transferred to 4" PIC wafers, and spectrally C- and L-band will be accessible thanks to the introduction of dedicated wide-gain active material.

**The SMART Photonics platform** will offer different versions of its platform. Next to a state-of-the-art high performance platform for data and telecom applications, a low-cost platform will be supported to focus on high volume applications in emerging areas such as sensing, imaging and healthcare. The wavelength band around 1.3 µm will be part of the new platform offering.

**The TriPleX platform** will offer process design kits also for other wavelength ranges and further integration of hybrid InP combinations is foreseen.

| Fraunhofer HHI                |                          |  |  |  |

|-------------------------------|--------------------------|--|--|--|

| Component                     | Expected performance     |  |  |  |

| EAM (phosphorus based)        | 56 GBd transmission rate |  |  |  |

| EAM (aluminum based)          | 70 GBd transmission rate |  |  |  |

| EOPM (phosphorus based)       | 56 GBd transmission rate |  |  |  |

| Improved polarization devices | >20 dB extinction ratio  |  |  |  |

| Out-of-plane coupling mirror  | 2 dB insertion loss      |  |  |  |

#### **SMART Photonics**

| Component                   | Expected performance     |

|-----------------------------|--------------------------|

| Spot-size converter         | < 1 dB insertion loss    |

| RF interconnects            | > 60 GHz 3-dB bandwidth  |

| Modulators (EAM and MZM)    | 56 GBd transmission rate |

| Photodetector               | > 50 GHz 3-dB bandwidth  |

| Electrical passive elements |                          |

| TriPleX                   |                                            |

|---------------------------|--------------------------------------------|

| Component                 | Expected performance                       |

| Arrayed-waveguide grating | ITU grid 8 and 16 channel                  |

| Micro rings               | single ring on ITU grid                    |

| PZT tuning elements       | $2\pi$ phase shift at $\mu W$ tuning power |

| Waveguides                | 0.1 dB/cm propagation loss                 |

**Table 4**List of platform components expected to be added by 2020.

#### Future Technology Nodes

As PIC technology development continues, novel schemes will emerge either to enable new applications by combining different technologies in a reliable way or to continue scaling the density of components for very large scale integrated (VLSI) photonic systems. Research lines are targeting new technology nodes within a period of five to ten years.

#### Hybrid InP-SiN integration

For both SiP and SiN, lasers and amplifiers have to be integrated in a hybrid way. By hybrid integration we understand an approach in which different chips are coupled after processing. Hybrid integration technology has made considerable progress. It is especially favourable where the PIC requires component properties which cannot be provided by a single platform, for example optical gain and very low loss. The integration of InP active components (lasers and modulators) is on the roadmap of LioniX International, and will be implemented in the TriPleX PDK and offered in MPW services

|                               | Performance |     |     |                        |                      |

|-------------------------------|-------------|-----|-----|------------------------|----------------------|

| Building Block                | InP         | SiP | SiN |                        |                      |

| Passive components            | ••          | ••  | ••• |                        |                      |

| Polarisation components       | ••          | ••  |     | Perfor                 | mance                |

| Lasers                        | •••         | н   | н   |                        | Very good            |

| Phase modulators              | •••         | ••  | •   |                        | , ,                  |

| Electro-absorbtion modulators | •••         | ••  |     | ••                     | Good                 |

| Switches                      | ••          | ••  | •   | •                      | Modest               |

| Optical amplifiers            | •••         | н   | н   | Fabrication Technology |                      |

| Detectors                     | •••         | ••  | н   | н                      | Hybrid/Heterogeneous |

#### Table 5 Performance comparison between three major platform technologies.

From table 5 it is seen that InP and SiN are perfectly complementary. A successful hybrid platform integrating InP and SiN components will offer, therefore, superior performance for both active and passive components and is a very promising approach for complex PICs which require very low propagation losses, e.g. in delay lines or high-Q filters. Ultra-low linewidth lasers by combining InP and TriPleX chips from LioniX and Fraunhofer HHI have recently been reported<sup>1</sup>. The TriPleX platform will not only allow the combination of efficient InP lasers with ultra low-loss passive waveguides, but it will also enable testing of InP circuits on wafer scale by using TriPleX-based optical waveguide probes.

#### Heterogeneous InP-Si electronics

By heterogeneous integration we understand an approach in which an unprocessed or partially processed wafer or die e.g. InP, is bonded to a processed wafer, e.g. silicon photonics or CMOS, and further processed on wafer scale after bonding. Heterogeneous integration of InP lasers and amplifiers on SiP circuits offers more flexibility in placement of lasers and amplifiers than hybrid integration, at the cost of added complexity in the fabrication process, because processing of both InP and SiP circuitry is now required. Further, the coupling between the InP and the SiP layer introduces coupling losses of 1 dB or more, and the coupling structures require significant space, of in the order of 100 µm per coupler depending on the substrate design.

<sup>1</sup> Integrated-photonics laser has record-narrow chip-based linewidth of 290 Hz http://www.laserfocusworld.com/articles/2017/07/integrated-photonics-laser-has-record-narrow-chip-based-linewidth-of-290-hz.html

Heterogeneous integration of InP-Photonics on Silicon Electronics avoids optical coupling losses as only one PIC technology is used, and offers high-performance electrical connections. To this end, JePPIX partners are working with microelectronics partners on a so-called Photronics platform. The approach consists in adapting the generic InP photonic integration process such as to make it suitable for wafer scale bonding onto a (Bi)CMOS wafer in which the driver, receiver and control electronics are integrated. The bonding is achieved by means of a polymer layer that is optically and thermally insulating, and thermal, mechanical and electrical connections are made with vias through the bonding layer. New components such as passive RF elements will be available either on electronic, photonic or intermediate layers, and building blocks for broadband interconnections will help improve integration density and circuit functionality. The photonic-electronic co-design will increase device speed and reduce power consumption. These efforts are expected to result in combined photonic-electronic MPW services in the longer term.

#### InP membrane on Silicon

The InP membrane on Silicon (IMOS) platform aims at further reducing the footprint of photonic devices by moving towards a high contrast waveguide technology embedded in an InP membrane that can be fabricated on Silicon wafers. It has seen significant progress since the start of the technology and now offers a range of passive waveguide components such as MMIs, ring resonators, directional couplers, dielectric and metallic grating couplers, and polarization converters. Lasers realized with active-passive integration have also been demonstrated recently. First experimental MPW runs with amplifiers and passive building blocks will be carried out in 2018 on a research basis. In 2020, it is planned to launch an experimental nano-photonic platform which includes optical amplifiers, high speed uni-travelling-carrier detectors and polymer-based slot-waveguide modulators, alongside the suite of existing active and passive building blocks.

## 6. Process Design Kit and Library Roadmap

Allowing designers to create a mask layout that can be submitted to a JePPIX foundry is one of the key elements of scalability of the generic integration technology. The introduction of Process Design Kits (PDK) back in 2008 together with the Multi Project Wafer (MPW) runs has largely supported the transition of PIC technology from academic research into commercial manufacturing. The potential of a foundry process is, to a large extent, determined by the maturity of the technology, reflected in the contents of the PDK. Such a PDK needs to be compatible with design software from several vendors and contains in general:

- Process information, describing a simple view of the mask layers involved in the fabrication process.

- Pre-defined mask layouts, specifications and models for a set of Basic Building Blocks (BBB).

- Mask layouts and models for a variety of more complex Composite Building Blocks (CBB) that can be grouped to form component libraries.

- A set of Design and Verification Rules

The set of Basic Building Blocks are enabled by the process technology as described in chapter 5 and their specifications are guaranteed by the foundry. A variety of CBBs can be created out of the BBBs, enriching the PDK content of the foundries, facilitating the design of application specific photonic circuits (ASPIC) and also forming proprietary component libraries. Both the set of BBBs and the component library that groups CBBs can be extended to hold simulation data in form of compact or physical models, which is in turn provided to simulation software tools.

#### Present Situation

Each of the three JePPIX foundries have a process design kit containing a component library of Basic Building Blocks and the most commonly used Composite Building Blocks. Since the 2015 roadmap release, more content has been added to the PDKs. Both InP foundries have included mask layouts and specifications for the newly developed technology components from chapter 5 such as transmitter (SOAs, lasers) and polarization handling blocks in the case of HHI and EAMs, gratings and detector building blocks in the case of SMART Photonics. LioniX is actively extending its PDK, adding more Composite Building Blocks for tele and datacom wavelengths and a version for visible light applications. An overview of the available library components is given in Table 6.

|      | SMART PDK                       | HHI PDK                           | Lionix PDK                  |

|------|---------------------------------|-----------------------------------|-----------------------------|

|      | WGs with 2 index contrasts      | WGs with 3 index contrasts        | Straight, arc, taper bend   |

|      | Straight, arc, taper bend       | Straight, arc, taper bend         | Spot size converter         |

|      | Photodetector                   | Spot size converter               | Phase modulator             |

|      | RF Photodetector                | Waveguide transitions             | Y-splitter                  |

|      | Semiconductor optical amplifier | MMI couplers                      | Directional coupler         |

|      | Mode filter                     | Photodetector variants            |                             |

| BBB  | DBR grating                     | Polarization components           |                             |

|      | Electro-absorption section      | Thermo-optic phase modulator      |                             |

|      | MMI reflectors                  | Current-injection phase modulator |                             |

|      | MMI couplers                    | Semiconductor optical amplifier   |                             |

|      | Waveguide transitions           | DFB laser                         |                             |

|      | Electro-optic phase modulator   | AWG                               |                             |

|      | AWG                             |                                   |                             |

| 000  | Electro-absorption modulator    | Electro-absorption modulator      | Mach-Zehnder interferometer |

| CBB  | Mach-Zehnder modulator          | DBR laser                         | Optical beamformer          |

|      | DC pad                          | DC pad                            | DC pad                      |

|      | RF pad                          | RF pad                            |                             |

| N.C. | RF CPW track                    | RF CPW track                      |                             |

| Misc | Waveguide crossing              | WG-metal crossing                 |                             |

|      | Electrical isolation            | Electrical isolation              |                             |

|      |                                 | Impedance matching RC             |                             |

#### **Table 6**Components offered in foundry PDKs.

Third-parties are engaged in creating more complex CBBs and grouping them into component libraries that complement the basic offering of the foundry PDKs. Custom passive components such as advanced AWGs, MMIs or active components such as widely tunable lasers and high-speed modulator modules from research institutions and design houses are being incorporated into these libraries, enabling more functionality and a speed up in the design process for end users. A standard framework to enable easy extension of the existing PDKs exists and is being improved to speed up the development of library components. In addition, generic

packaging templates and standards have been integrated and made available for the main packaging partners through collaborations in European projects such as through the PIXAPP project.

The design manuals for the generic foundry processes contain the performance parameters of most of the offered components but the specifications are not fully complete yet. Furthermore, the effects of statistical variations need to be reflected in the specifications. To have complete and reliable statistical data, automated building block characterization and performance tracking will become standard procedures.

#### Standardized Interface

The concept of the component library that can be filled by third-parties with advanced CBBs is of high importance for the generic foundry model and has the prospect of becoming a business of its own as is the case in the electronic integration industry. Presently, not many CBBs are easily available to all users as they are developed in different tools. To maintain a continuous growth of library content, assuring compatibility of the PDK with design and simulation tools from different vendors is crucial. Therefore a common framework is necessary in which design software can interface with foundry PDKs and communicate with each other. The PDAFlow API, as developed within EU-funded projects and now managed by the PDAFlow Foundation, has taken a central role in providing such a common framework, which is described in the next chapter in more detail. With the increase in the number of components and tool providers, it has to be extended to incorporate the interfacing with simulation models and the support of a licensing model for IP building blocks. To address these aspects work on an open PDK standard with an efficient version control and governance structure is required. Furthermore, convergence of this PDK standard with its electronic counterpart to facilitate the trend towards integration of photonics with electronics is necessary and will be worked on.

#### Roadmap 2020

The process design kit will contain statistical data on mean values and 3 sigma control limits for each BBB, determined from a series of fabrication runs by automatically measuring in-line and off-line test structures. Calibration data for simple compact models will be incorporated into the PDK that relate design variation and fabrication tolerances to device performance and that are seamlessly integrated with simulation tools through a common data exchange standard.

More advanced CBBs will be developed and made available for different application sectors, e.g. for communications, microwave photonics and optical sensing. IQ vector modulators and coherent receivers operating at 25 Gb/s together with tunable lasers < 300 kHz linewidth will be offered with < 1 pJ/bit transmit power efficiency. Widely tunable laser modules with > 40 nm tuning and > 3mW output power and pulsed lasers with adjustable repetition rate up to 30 GHz will be available. High speed receivers (50 GHz) with saturation input powers up to 10 mW will be part of the offering. The open PDK framework will be accepted as a standard and additional CBBs originating from the pool of ASPIC designs from the eco-system will complement the library offer.

In addition, generic test templates will be added to the libraries, facilitating optical and electrical testing and packaging. This involves templates for DC and RF pad placement but also schemes for edge and vertical fibre-to-chip coupling to assist standardized packaging and on-wafer testing.

#### Roadmap 2022

The amount of available statistical performance data will be extended to the component library and its CBBs with compact models describing their behaviour. Seamless integration of the PDK into the design workflow with a standardized PDK structure and data transfer formats will be implemented and maintained in an open environment. This will allow accurate and fast modelling of passives and actives in circuit simulation tools, with calibrated compact models. In addition, test procedures can be defined during the chip design phase and performed virtually in design and simulation tools.

Initial interfaces to electronic PDKs will be established to enable the co-design of electronic and photonic circuits. Modulator and detector CBBs will have corresponding driver and receiver building blocks in the respective electronic PDKs with simple co-simulation models attached. In addition, interconnection building blocks and passive RF components will be provided to support the heterogeneous integration technology.

## 7. Photonic IC Design Tools and Flows Roadmap

#### PDKs and Layout

As described in chapter 6, the introduction of PDKs and MPWs has fuelled innovation in the domain of integrated photonics technology. The effective sharing of key information within the design community enabled engineers with little understanding of the actual fabrication technology to make designs that deliver the required functionality and are actually manufacturable. As mentioned before, the description of mask layouts for various basic and composite building blocks allowed designers to pick, place and connect blocks to create functions for a specific application. To allow for customized design within the boundary conditions of a particular process, the PDK needs to hold information that can help designers to validate the manufacturability of their designs. Adding these so called design rules to photonic PDKs is now also common practice in the electronics industry.

#### Design Rule Checking

Design rule checking needs to be implemented on two levels. First, the mask layout software implements design intent checking, by ensuring that parameters are within the range as specified in the Design Manual and that basic rules for good circuit design are followed. Some of these are presently in place and give an early warning to designers if rules are not followed. Secondly, the resulting GDSII mask files themselves are submitted to Design Rule Check (DRC). This will mostly flag violations of (technology) rules set by the foundries. A number of such DRCs are presently in place for the JePPIX foundries. A much more extensive set of such DRCs is being developed, and checking should be an automated service performed by software tools, since manual checking is labour-intensive and error-prone.

#### Component Modelling

Models for both frequency domain as well as time-domain circuit simulation are becoming available, to enable a full design flow from circuit design to verified layout. To further develop the automation of designing photonic integrated circuits and systems, tools and flows activities are ongoing at several software vendors, design houses and academia, supporting PDK driven as well as custom design within the boundaries of the generic fabrication technology.

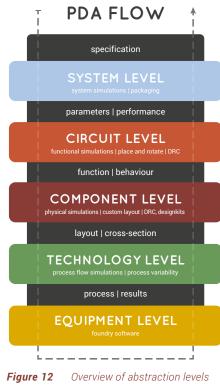

Depending on the end-application and complexity of the design (e.g. the number of components, or the balance between photonic and electronic components) the most applicable tools or flow might be different. The picture below depicts the different abstraction levels in the full design flow and is used to illustrate the development focus points for the coming years.

*Figure 12* Overview of abstraction levels in the PIC design flow.

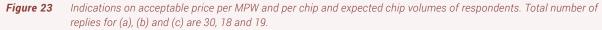

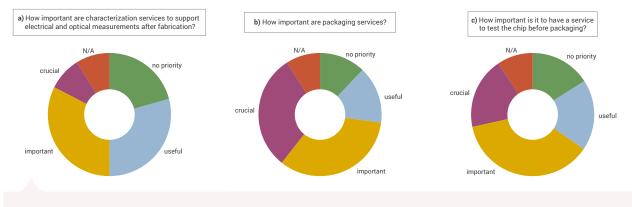

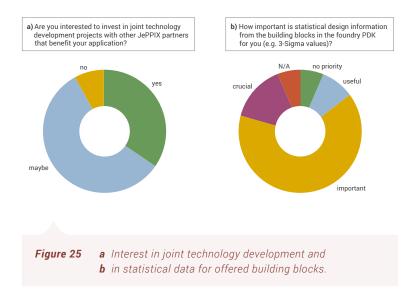

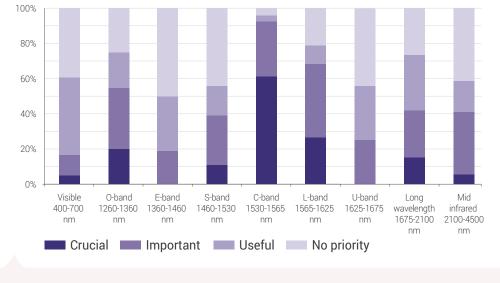

#### Present situation 2018